ARM بهتازگی از هستههای پردازشی Cortex-A75 ،Cortex-A55 و هستههای گرافیکی Mali-G72 برای استفاده در دستگاههای موبایل رونمایی کرده است. هستههای جدید ARM برمبنای معماری ARMv8.2-A برای استفاده در نسل جدید سیستمهای روی چیپ (SoC) طراحی شدهاند. باتوجه بهاینکه این هستهها قرار است در قلب بسیاری از پردازندههای جدید از جمله اسنپدراگون 845 کوالکام قرار بگیرند، و ازطرفی با توجه به اعلام کوالکام و مایکروسافت مبنی بر اجرای نسخهی کامل ویندوز 10 روی این پردازندهها، آشنایی با معماری هستههای ARM بسیار مفید خواهد بود.

بههمین منظور قصد داریم طی مقالهای سه قسمتی در زومیت، به بررسی دقیق جزئیات فنی و ویژگیهای جدید معماری هستههای کورتکس ARM بپردازیم. قسمت اول این مجموعه به بررسی تکنولوژی DynamIQ (بخوانید داینامیک) اختصاص دارد.

مقدمه

ARM با توجه به نیاز شرکای سختافزاری خود و پیشرفت سریع دستگاهها در قسمتهایی مانند نمایشگر و هوش مصنوعی، مجبور است ریزمعماری پردازندههای خود را بهصورت سالانه بهروزرسانی کند. بههمین منظور، چندین تیم توسعه در نقاط مختلف دنیا بهصورت موازی و همزمان مشغول کار روی طراحیهای جدید برای ARM هستند.

سال گذشته در جریان کنفرانس سالانهی TechDay در آستین تگزاس، ARM از هستههای گرافیکی Mali-G71 با معماری جدید Bitfrost و هستههای پردازشی Cortex-A73 بهعنوان جایگزینی برای A72 رونمایی کرد. نکتهی قابل توجه درجریان رونمایی از هستههای جدید در سال گذشته، عدم معرفی هستههای LITTLE در کنار هستههای big کورتکس A73 بود. (در معماری big.LITTLE، از تعدادی هستهی قوی (big) در کنار هستههای ضعیف و کممصرف (LITTLE) استفاده میشوند.)

در جریان TechDay امسال که در کمبریج انگلستان برگزار شد، ARM از هستههای گرافیکی جدید Mali-G72، هستههای پردازشی Cortex-A75 و درنهایت بالاخره از جانشین هستههای LITTLE کورتکس A53 با نام A55 رونمایی کرد.

A53 همزمان با هستهی A57 معرفی شده بود و چندین سال است که بهصورت مستقل، یا به عنوان هستهی LITTLE در چیپهایی که از معماری big.LITTLE بهره میبرند، استفاده میشود. کورتکس A53 که ظرف مدت کمتر از 3 سال، 1.7 میلیارد نسخه از آن در محصولات ساخت 40 شرکت استفاده شده است، یکی از موفقترین هستههای ARM تا بهامروز بهشمار میرود؛ اما عدم معرفی هستهی LITTLE جدید طی چند سال گذشته، باعث شده است تا فاصلهی قدرت پردازشی این هسته با هستههای big بسیار زیاد شود.

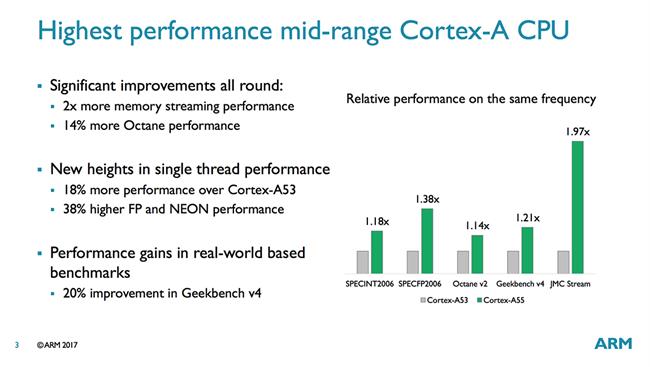

مقایسهی عملکرد A55 با A53 در فرکانس یکسان

عملکردهای مرتبط با مموری در Cortex-A55 تا دو برابر نسبت به A53 بهبود پیدا کرده است

ازآنجاییکه A53 از قبل عملکرد پردازشی نسبتا خوبی را دراختیار میگذاشت، اینبار با معرفی A55، تمرکز ARM روی بهبود سیستم مموری هستههای جدید بوده است. استفاده از کش L2 با تأخیر 50 درصد کمتر نسبت به نسل قبل، بهکارگیری کش L3 برای اولین بار و دیگر بهبودهای مموری محور، باعث شده است تا عملکردهای مرتبط با مموری در A55 شاهد بهبود دو برابری در بنچمارک LMBench باشد. اعداد ارائه شده توسط ARM همچنین حاکی از بهبود 18 درصدی در بنچمارک SPECint 2006 و بهبود 38 درصدی در SPECfp 2006 هستند.

این مقادیر و درصدهای نشاندادهشده در نمودارها، همگی مربوط به مقایسهی A53 و A55 با فرکانس، کش L1 و L2 و کامپایکر کاملا یکسان است. ازآنجایی که سازندگان تراشه احتمالا از فرکانس بالاتر به همراه مقداری کش L3 در SoC-های مبتنی بر A55 استفاده خواهند کرد، نتایج واقعی احتمالا از اعداد و ارقام ارائه شده توسط ARM نیز بهتر خواهد بود.

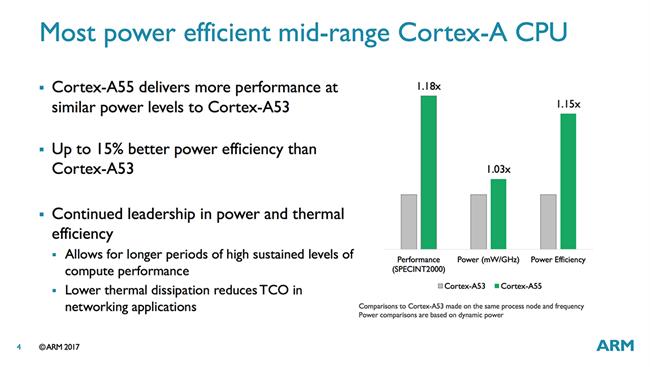

مقایسهی توان، عملکرد و بهینگی مصرف انرژی هستههای A53 و A55

این افزایش عملکرد البته باعث افزایش 3 درصدی مصرف انرژی در هستههای A55 شده است؛ اما با توجه به نتایج بنچمارک SPECint 2000، در عین حال بهینگی مصرف انرژی نیز 15 درصد بهبود یافته است.

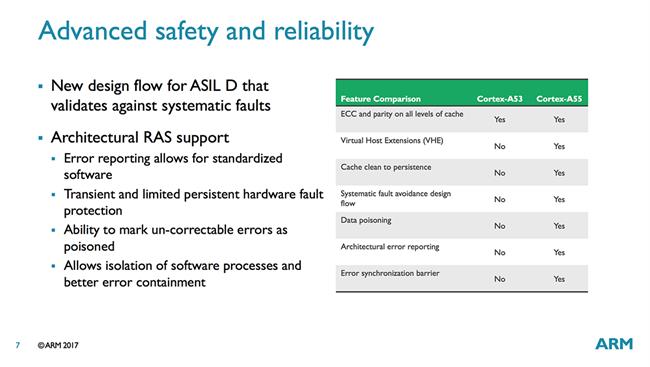

A55 همچنین به قابلیتهایی جدید برای استفاده در دستگاههایی بهغیر از تلفنهای هوشمند مجهز شده است. برای مثال Virtual Host Extensions) VHE) و پشتیبانی از سرویسهای دسترسی از راه دور (RAS)، از جمله قابلیتهای جدیدی هستند که برای خودروهای خودران بسیار مهم بهشمار میروند و اضافه شدن مجموعه دستورالعملهای ضرب نقطهای Int8 (مجموعهای از دستورالعملهای جدید برای یادگیری عمیق)، A55 را برای استفاده در شبکههای عصبی مناسب میکند. همچنین ازآنجایی که A55 با DynamIQ سازگار است، میتواند به پورتهای 256 بیت AMBA 5 CHI نیز درسترسی داشته باشد.

مجموعهای از قابلیتهای جدید هستههای کورتکس که به «امنیت» و «پایداری» سیستم کمک میکند.

هنگامی که ARM سال گذشته هستههای A73 را معرفی کرد، روی قابلیت «عملکرد پایدار» هستههای جدید خود مانور زیادی داد. این قابلیت که در نسل جدید هستههای ARM نیز حضور دارد، باعث میشود هنگام پردازش سنگین در بازههای زمانی طولانی، عملکرد پردازنده ثابت باقی بماند و دچار افت نشود. درحالیکه ARM در طراحی A73 تمرکز اصلی خود را روی بهبود مصرف انرژی هسته قرار داده بود، در A75 با نگهداشتن بهینگی انرژی در سطحی برابر با A73، عملکرد پردازشی هسته را افزایش داده است.

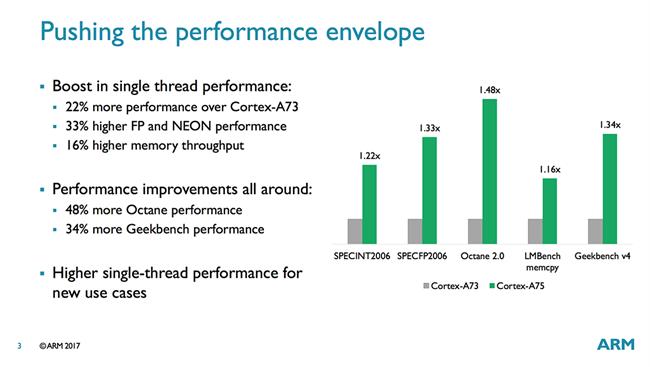

عملکرد هستهی A75 در مقایسه با A73 افزایش قابل توجهی داشته است.

A73 بهدلیل بهرهگرفتن از معماری کاملا متفاوت با A72، نتایج نسبتا عجیبی در بنچمارکها از خود نشان میداد. درحالی که عملکرد محاسبات صحیح (Integer Performance) هستهی جدید نسبت به A72 بهبود پیدا کرده بود، اما در محاسبات ممیز شناور A73 شاهد افت عملکرد نسبت به هستههای قدیمی بود. خوشبختانه ظاهرا این مشکل در A75 برطرف شده است؛ چرا که باتوجه به اعداد ارائه شده توسط ARM، هستههای A75 هم در محاسبات صحیح و هم ممیز شناور، بهبود قابل توجهی نسبت به A73 دارند.

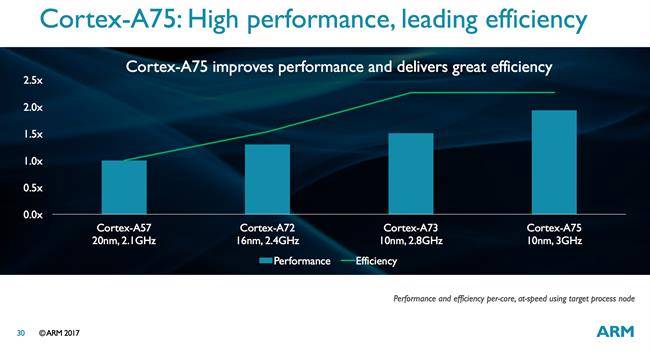

مقایسهی عملکرد و بازده هستههای A57، A72، A73 و A75

نمودار بالا نشان میدهد که A75 در سرعت کلاک 3 گیگاهرتز روی گرههای 10 نانومتری، عملکردی بهتر از هستههای A73 در کلاک 2.8 گیگاهرتز روی گرههایی با همان اندازه از خود نشان میدهد، و در عینحال بازده انرژی آن نیز ثابت باقی مانده است. این به معنی افزایش مصرف انرژی هستههای جدید است. برای کنترل کردن دمای تولید شده توسط پردازنده، ARM در A72 هنگام استفاده از 4 هسته بهصورت همزمان، عملکرد هسته را در یک بازهی ترمالِ مشخص محدود کرده بود. ARM در A75 نیز برای دستیابی به عملکرد پایدار، از تکنیک «بازهی ترمال تعریف شده» استفاده کرده است. البته استفاده از هر 4 هسته بهصورت همزمان سناریوی متداولی در تلفنهای هوشمند نیست، چراکه اکثر برنامههای موبایل نهایتا از یک تا دو هسته بهصورت همزمان، آنهم در بازههای کوتاه زمانی استفاده میکنند.

ARM در A75 محدودیت مصرف 750 میلیواتی هسته را برداشته است؛ اما با افزایش توان هسته از 1 به 2 وات،

تنها شاهد افزایش 5 درصدی عملکرد آن هستیم.

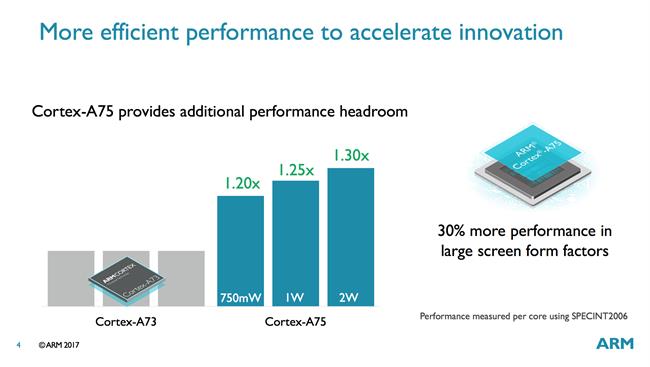

ARM همچنین با افزایش فرکانس و عبور از سد محدودیت توان مصرفی 750 میلیوات در هر هسته، قصد دارد A75 را به گزینهای برای استفاده در دستگاههایی با فرمفاکتور بزرگتر تبدیل کند. با این کار، استفاده از هستههای A75 در کرومبوکها و لپتاپهای ویندوزی (در صورت ارائهی ویندوز 10 سازگار با ARM توسط مایکروسافت) ممکن میشود.

ARM با افزایش توان مصرفی هستههای جدید، آنها را برای استفاده در لپتاپها آماده کرده است

افزایش توان مصرفی به 1 وات بر هسته، باعث میشود عملکرد A75 تا 25 درصد نسبت به A73 بهبود پیدا کند؛ اما با افزایش توان به 2 وات بر هسته، تنها شاهد افزایش 30 درصدی عملکرد هستههای جدید خواهیم بود. این اعداد و ارقام یکی از بهترین مثالها برای نشان دادن این اصل مهم هستند که «افزایش صرف فرکانس هسته به معنی بهبود عملکرد پردازشی CPU نیست»؛ چرا که با بالارفتن سرعت کلاک، مصرف انرژی بهصورت لگاریتمی بالا میرود.

ARM با تمرکز بر بهینگی مصرف انرژی، ویژگیهایی مانند استفاده از ECC در کش L1 و دسترسی به پورت 256 بیتی AMBA 5 CHI را بهمنظور کاهش پیچیدگی طراحی هسته از A73 حذف کرده بود؛ چرا که قصد داشت پردازندهای کممصرف و ساده دراختیار تولیدکنندگان دستگاههای موبایل قرار بدهد. با معرفی هستههای جدید اما ARM با گنجاندن ویژگیهای متعدد در A75، آن را برای استفاده در سرورها، خودروهای خودران و دیگر مصارف آماده کرده است.

DynamIQ

بهزبان ساده، DynamIQ نسخهی جدید big.LITTLE است

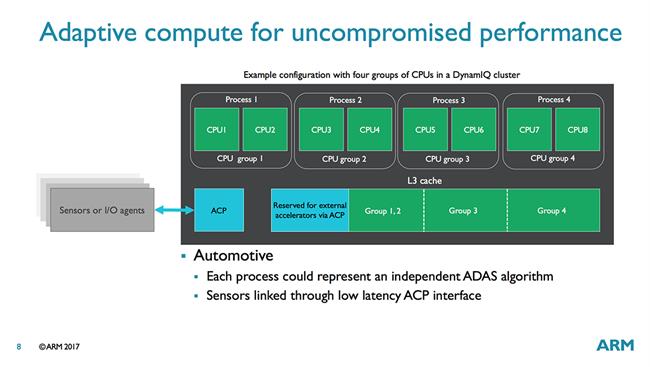

تکنولوژی big.LITTLE آرم که 5 سال پیش معرفی شد، اجازه میداد تا چندین کلاستر (تا 4 CPU) بهصورت زنجیرهای با هم ترکیب شوند. با استفاده از big.LITTLE این امکان بهوجود میآمد تا ترکیبهای مختلفی از هستههای خانوادهی Cortex-A درکنار یکدیگر بهکار گرفته شوند و درنتیجه ساخت طیف وسیعی از پردازندهها (از پردازندهی تلفنهای پایینرده و مقرونبهصرفه گرفته تا دستگاههای پرچمدار گرانقیمت) میسر میشد.استفاده از تکنولوژی big.LITTLE برای ترکیب هستههای کورتکس تنها به تلفنهای هوشمند و تبلتها محدود نمیشد؛ بلکه طی این سالها شاهد استفاده از پردازندههای مبتنی بر این تکنولوژی در سرورها و خودروهای خودران نیز بودهایم.

با تغییر ساختار و کارایی دستگاههای مبتنی بر ARM طی سالهای اخیر، نیاز به تکامل تکنولوژی big.LITTLE بهشدت احساس میشد. ARM نیز که بهتر از همه به این موضوع واقف بود، همزمان با رونمایی از جدیدترین هستههای خود، نسخهی جدید big.LITTLE را با نام DynamIQ معرفی کرد. بهگفتهی ARM، توسعهی DynamIQ از سال 2013 شروع شده و از آن زمان تاکنون، تغییرات زیادی بهخود دیده است. باتوجه به زمان نسبتا طولانی توسعهی DynamIQ، انتظار میرود تا چندین سال شاهد استفادهی بدون تغییر از آن در پردازندههای ARM باشیم.

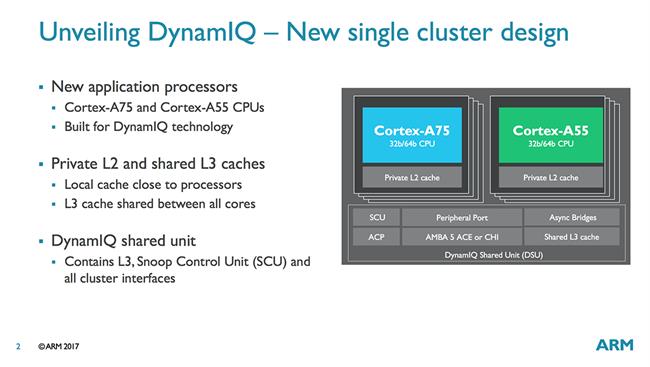

با استفاده از DynamIQ میتوان هستههای big و LITTLE را با کش اختصاصی در یک کلاکستر استفاده کرد

درست مانند big.LITTLE، تکنولوژی DynamIQ نیز امکان گروهبندی CPU در کلاستر و متصل کردن آن به دیگر پردازندهها (برای مثال پردازندهی گرافیکی) و دیگر سختافزارهای سیستم را فراهم میکند؛ اما تفاوتهای بزرگی در نحوهی انجام این کار بین دو تکنولوژی مذکور وجود دارد. برای شروع، بزرگترین تغییر ایجاد شده در DynamIQ، امکان استفادهی همزمان از هستههای big و LITTLE در یک کلاستر است. (تا پیش از این هستههای کورتکس متفاوت باید در کلاسکرهای جدا از هم استفاده میشدند.) همین تغییر بهظاهر ساده، علاوه بر بالابردن عملکرد پردازنده، دست سازندگان SoC را برای بهکارگیری ترکیبهای بسیار متنوعتر از هستهها باز خواهد گذاشت.

بزرگترین ویژگی DynamIQ، امکان استفاده از هستههای متفاوت در کنار یکدیگر، درون یک کلاستر است

تغییر بزرگ بعدی، امکان گنجاندن تا 8 CPU در یک کلاستر، و افزایش ماکزیمم تعداد کلاسترها به 32 عدد است. درنتیجه با استفاده از تکنولوژی DynamIQ میتوان تا 256 CPU را در یک چیپ جای داد.

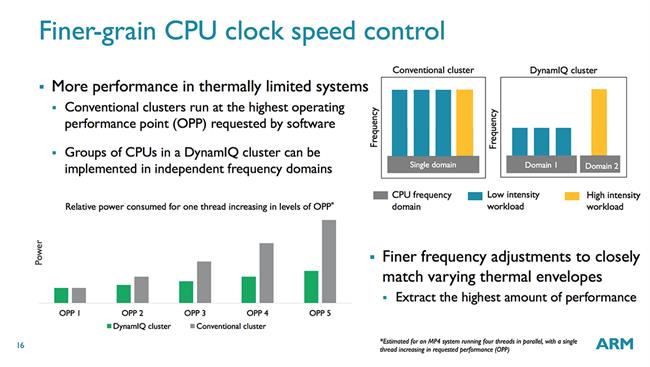

درون هر کلاستر، CPU بر اساس ولتاژ یا فرکانس در دامنههای متفاوت تقسیمبندی میشوند و درون هر دامنه، هستهها با توجه به توان مصرفی درون زیردامنههای خود قرار میگیرند. این کار باعث میشود بتوان مصرف هر CPU را جدا از CPU-های دیگر، بهصورت مجزا کاهش یا افزایش داد. با استفاده از DynamIQ هر کلاستر میتواند تا 8 ولتاژ یا فرکانس متفاوت را پشتیبانی کند.

آنچه در بالا گفته شد به بیان ساده یعنی در حالت تئوری، سازندگان SoC قادر خواهند بود تا CPU-هایی با ولتاژ و فرکانس متفاوت و مستقل از یکدیگر را درون یک کلاستر قرار بدهند. این موضوع باعث میشود یک هستهی پرمصرف، ولتاژ و فرکانس بالای خود را به هستههای کممصرف تحمیل نکند و درنتیجه بهینگی مصرف انرژی دستگاه تا حد زیادی بهبود پیدا کند. البته هر دامنهی فرکانسی به رگولاتور ولتاژ مخصوص به خود نیاز دارد که موجب افزایش هزینه و پیچیدگی طراحی SoC خواهد شد. برای همین، احتمالا مانند سابق شاهد استفاده از حداکثر 2 تا 4 CPU در هر کلاستر خواهیم بود.

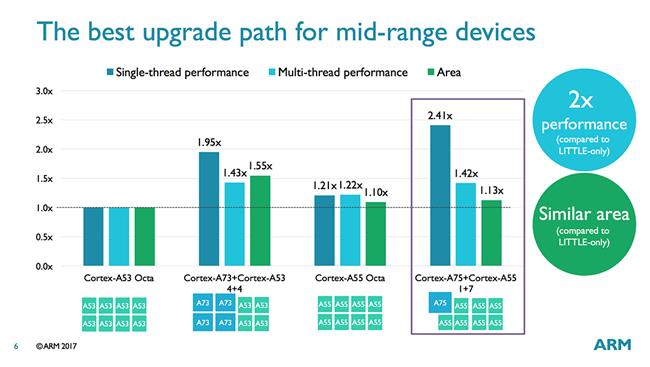

مقایسهی عملکرد ترکیبهای مختلف هستههای کورتکس در یک پردازندهی 8 هستهای

ARM عقیده دارد طی سالهای آینده، صنعت موبایل همچنان شاهد استفاده از پردازندههای 8 هستهای در دستگاههای موبایل خواهد بود. تاکنون با استفاده از تکنولوژی big.LITTLE، ترکیب 8 هسته یا بهصورت 4+4 (که در آن از 4 هستهی big در کنار 4 هستهی LITTLE در دو کلاستر استفاده میشد) در دستگاههای بالارده، یا بهصورت استفاده از 8 هستهی LITTLE در دستگاههای پایینرده بوده است. با تکنولوژی DynamIQ اما هستههای A75 یا A55 میتوانند با هر ترکیب دلخواهی (برای مثال 1+7، 2+6، 3+5 و 4+4) درون یک کلاستر در کنار یکدیگر قرار بگیرند.

ARM عقیده دارد از میان ترکیبهای ممکن، ترکیب 7 هستهی کممصرف A55 با یک هستهی big از نوع A75 برای دستگاههای میانرده بسیار مناسب خواهد بود؛ چرا که تنها با افزایش 1.13 برابری مساحت تراشه، عملکرد تکهستهی آن 2.41 برابر و عملکرد چند هستهای آن 1.42 برابر نسبت به پردازندههایی که هر 8 هستهی آنها A53 (با کلاک برابر) است، افزایش خواهد یافت.

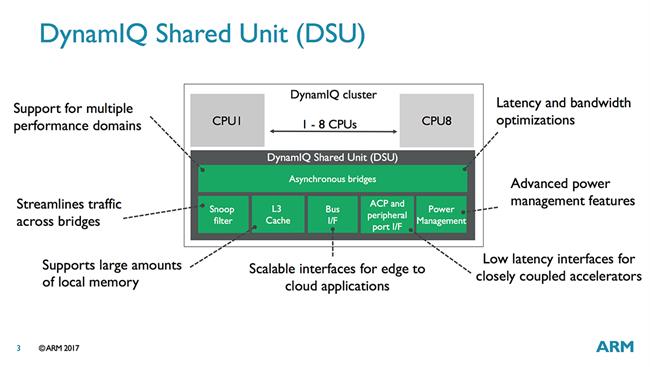

DSU نام بلوک جدیدی در معماری ARM است که حافظهی کش L3 درون آن قرار دارد

مهمترین قطعهی پازل DynamIQ، که باعث میشود هستههای پردازشی درون یک کلاستر بتوانند در فرکانسهای متفاوت و مستقل از یکدیگر کار کنند، بلوک جدیدی با نام DynamIQ Shared Unit) DSU) است. بلوک DSU درواقع نقش یک هاب مرکزی را در هر کلاستر بازی میکند که هستهها با ولتاژهای مختلف، از طریق آن با بقیهی سیستم ارتباط برقرار میکنند.

کش L3 بهکار رفته در DSU از نوع شبهاختصاصی است

بلوک DSU نقش هاب مرکزی کلاستر را بازی میکند و کش L3 و بسیاری ویژگیهای دیگر درون آن قرار دارد

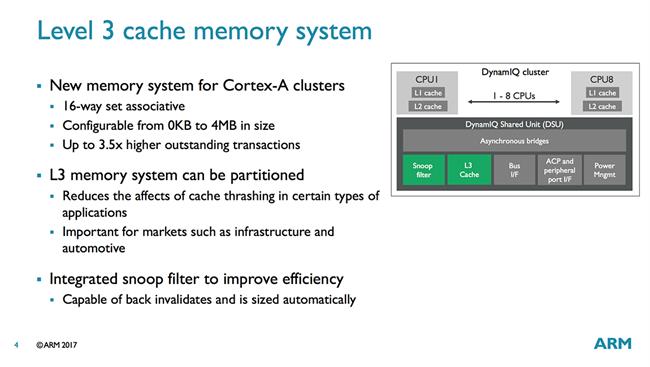

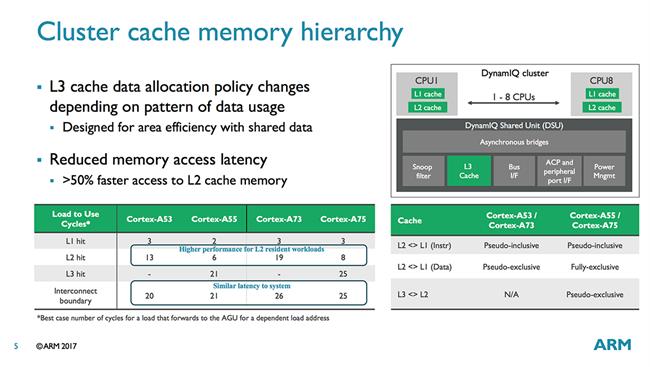

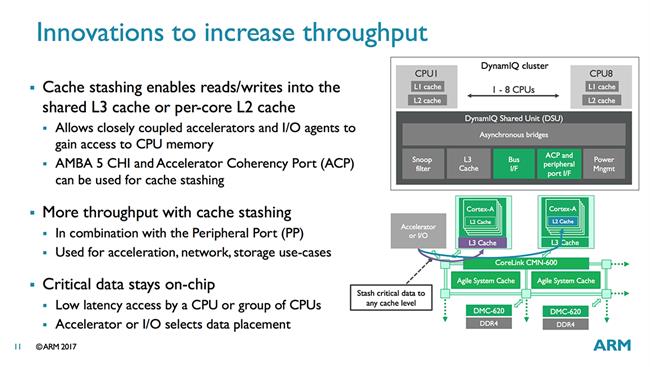

تا بهحال هرچه از DynamIQ گفتیم مربوط به توانایی آن در بهکارگیری هستههای مختلف درکنار یکدیگر بوده است. اما این تکنولوژی علاوه بر ایجاد انعطاف در ترکیب هستههای درون یک کلاستر، بهبود عملکرد CPU را نیز با خود به ارمغان میآورد. با استفاده از تکنولوژی big.LITTLE،اCPU-های درون یک کلاستر میتوانستند بهصورت اشتراکی از یک کش L2 استفاده کنند؛ اما با آمدن DynamIQ،اCPU-های سازگار با این تکنولوژی (درحال حاضر تنها A75 و A55) امکان دسترسی به کش L2 اختصاصی، با فرکانس برابر با هستهی خود را دارند. انتقال کش L2 به نزدیکی هسته، میزان تأخیر آن را تا 50 درصد کاهش میدهد. DynamIQ همچنین سطح جدیدی از کش را به تراشه اضافه میکند. کش L3 اضافه شده که استفاده از آن توسط سازندگان SoC اختیاری خواهد بود، درون DSU قرار میگیرد. مقادیر کش L3 در معماری جدید ARM میتواند 1، 2 یا 4 مگابایت باشد و بهصورت اشتراکی از آن استفاده خواهد شد.

کش L3 بهصورت کلی میتواند «فراگیر» یا «اختصاصی» باشد. کش L3 فراگیر یک کپی کامل از کش L2 پردازنده را نیز درخود جای میدهد که باعث کاهش شدید عملکرد و هدر رفتن فضا و توان مصرفی آن میشود. گرچه حافظهی کش L3 بهکار رفته در DSU-های ARM از نوع «شبه اختصاصی» است، اما ARM ادعا میکند این حافظه به کشهای L3 اختصاصی بسیار نزدیکتر است تا فراگیر.

آوردن کش L2 به درون کلاستر و قرار دادن آن در نزدیکی هسته، میزان تأخیر آن را تا 50 درصد کاهش میدهد

کش L3 درون DSU میتواند پارتیشنبندی شود که برای استفاده در سامانههای نهفته (امبدد) که بار کاری ثابتی دارند، بسیار مفید خواهد بود. این حافظه میتواند به 4 پارتیشن با سایزهای متفاوت تقسیم شود، درنتیجه یک CPU میتواند مثلا از 3 مگابایت، و هفت CPU دیگر در مجموع از 1 مگابایت کش L3 بهصورت اشتراکی استفاده کنند.این پارتیشنها از نوع دینامیک خواهند بود و میتوان حین اجرای برنامهها توسط سیستم عامل آنها را تولید یا تغییر اندازه داد.

قابلیت «ذخیره روی کش»، امکان دسترسی سختافزارهای خارج از کلاستر به کش L2 و L3 را فراهم میکند

از دیگر ویژگیهای DynamIQ میتوان به قابلیت «ذخیره روی کش» (cache stashing) اشاره کرد که به GPU یا دیگر شتابدهندههای سختافزاری و ایجینتهای I/O اجازه میدهد تا از طریق رابط ACP یا پورت AMBA 5 CHI بهصورت مستقیم اطلاعات را روی کش L2 و L3 بنویسند یا از روی آن بخوانند. به عنوان مثال میتوان به عملکردهای مرتبط با شبکه اشاره کرد که در آنها با استفاده از مجموعه پروتکلهای TCP/IP، پَکِتهای شبکه پردازش میشوند. در این حالت موتور شتابدهنده بهجای نوشتن دادهها روی رم سیستم (یا هر مکانیزم کش دیگر) و سپس منتقل کردن آن به CPU برای پردازش، میتواند با استفاده از قابلیت ذخیره روی کش، دادهها را بهصورت مستقیم روی کش L2 پردازنده بنویسد. با این کار عملکرد طیف وسیعی از برنامهها افزایش، و مصرف انرژی کاهش پیدا میکند.

با استفاده از قابلیت ذخیره روی کش (cache stashing)، سختافزارهای خارج از کلاستر نیز میتوانند به کش L2 و L3 دسترسی داشته باشند.

برای استفاده از قابلیت ذخیره روی کش، درایورهای نرمافزاریِ کرنل باید از پردازنده و توپولوژی کش آگاه باشند؛ درنتیجه برای فراهم کردن امکان دسترسی سختافزارهای خارج از کلاستر به کش L2 اشتراکی، نیاز به اضافه کردن کدهای اختصاصی جدید به درایورهای نرمافزاری وجود دارد. ازآنجاییکه بسیاری از دستگاههای مصرفی مانند تلفنهای هوشمند همواره با مشکل «محدودیت زمانی» برای عرضه به بازار روبهرو هستند، شاید بسیاری از تولیدکنندگان زحمت اضافه کردن کد برای استفاده از این قابلیت را بهخود ندهند و درنتیجه موج اول دستگاههای مجهز به هستههای جدید ARM از این قابلیت جدید و کاربردی محروم باشند.

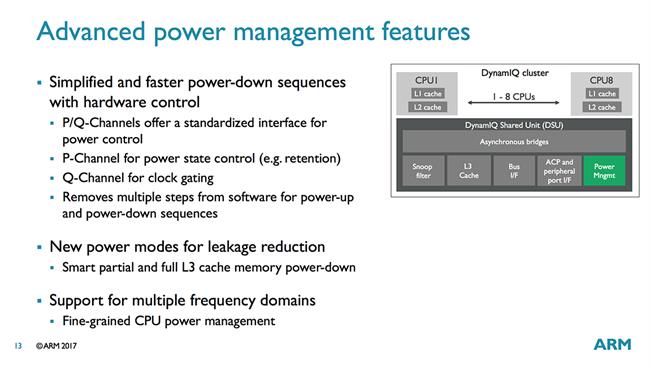

یکی از ویژگیهای بلوک DSU، مدیریت سختافزاری توان مصرفی پردازنده است

DynamIQ دارای مجموعهای از قابلیتهای پیشرفته، برای مدیریت توان پردازنده است

علاوه بر اشتراک منابع با سختافزارهای خارج از کلاستر، DynamIQ اشتراک داده بین CPU-های درون یک کلاستر را نیز راحتتر کرده است. همین موضوع مهمترین دلیلی بود که ARM را بر آن داشت تا CPU-های big و LITTLE را این بار درون یک کلاستر در کنار هم قرار دهد. انتقال اطلاعات کش درون یک کلاستر بسیار سریعتر از انتقال آن بین دو یا چند کلاستر است و علاوه بر آن زمان تأخیر کش نیز بسیار کاهش پیدا میکند.

DynamIQ همچنین دارای مجموعهای از ویژگیهای پیشرفته برای مدیریت مصرف انرژی پردازنده است. برای مثال، مدیریت کش در معماری جدید توسط DSU و بهصورت سختافزاری انجام میشود. برخلاف مدیریت نرمافزاری، هنگام تغییر دادن وضعیت توان CPU توسط DSU و بهصورت سختافزاری، احتیاج به طی مراحل اضافه از بین میرود و درنتیجه میتوان قدت هستههای CPU را بسیار سریعتر از پیش افزایش یا کاهش داد.

ازآنجایی که بهکاربردن تکنولوژی جدید در پردازندهها نیازمند صرف زمان و هزینه است، شاید برخی تولیدکنندگان SoC ترجیح بدهند همچنان از تکنولوژی big.LITTLE در سیستمهای روی چیپ خود استفاده کنند. اما ازآنجایی که استفاده از تکنولوژی جدید با نامی پرطمطراق میتواند از لحاظ بازاریابی محصول به نفع تولید کننده تمام شود (مخصوصا در تلفنهای هوشمند پرچمدار)، احتمالا در آیندهای نزدیک شاهد بهکارگیری این تکنولوژی در پردازندهی دستگاههای بالارده خواهیم بود. انتظار میرود اولین SoC-های مجهز به تکنولوژی DynamIQ در اواخر سال 2017 یا اوایل 2018 به بازار عرضه شوند.

در قسمت بعدی با ریزمعماری هستههای Cortex-A75 بیشتر آشنا خواهیم شد.